EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 609

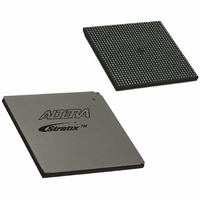

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 609 of 864

- Download datasheet (11Mb)

Altera Corporation

September 2004

Implementing High Performance DSP Functions in Stratix & Stratix GX Devices

Polyphase Decimation Filter Implementation Results

Table 7–14

implementation in a Stratix device shown in

Polyphase Decimation Filter Design Example

Download the Decimation FIR Filter (decimation_fir.zip) design

example from the Design Examples section of the Altera web site at

www.altera.com.

Complex FIR Filter

A complex FIR filter takes real and imaginary input signals and performs

the filtering operation with real and imaginary filter coefficients. The

output also consists of real and imaginary signals. Therefore, a complex

FIR filter is similar to a regular FIR filter except for the fact that the input,

output, and coefficients are all complex numbers.

One example application of complex FIR filters is equalization. Consider

a Phase Shift Keying (PSK) system; a single complex channel can

represent the I and Q data channels. A FIR filter with complex coefficients

could then process both data channels simultaneously. The filter

coefficients are chosen in order to reverse the effects of intersymbol

interference (ISI) inherent in practical communication channels. This

operation is called equalization. Often, the filter is adaptive, i.e. the filter

coefficients can be varied as desired, to optimize performance with

varying channel characteristics.

A complex variable FIR filter is a cascade of complex multiplications

followed by a complex addition.

representation of a complex FIR filter. To compute the overall output of

the FIR filter, it is first necessary to determine the output of each complex

multiplier. This can be expressed as:

Note to

(1)

Part

Utilization

Performance

Table 7–14. Polyphase Decimation Filter Implementation Results

This refers to the performance of the DSP blocks, as well as the input clock rate.

The output rate is 60 MSPS (clocked out at 60MHz).

Table

shows the results of the polyphase decimation filter

7–14:

EP1S10F780

Lcell: 168/10570 (1%)

DSP Block 9-bit elements: 8/48 (17%)

Memory bits: 300/920448(<1%)

240 MHz

(1)

Figure 7–18

Stratix Device Handbook, Volume 2

Figure

shows a block diagram

7–17.

7–31

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: