EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 675

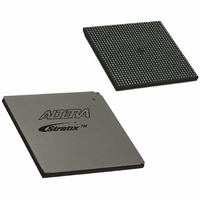

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 675 of 864

- Download datasheet (11Mb)

Altera Corporation

July 2005

Interface Implementation in Stratix & Stratix GX Devices

The 16-bit full-duplex LVDS implementation of the framer part of the

SFI-4 interface is shown in

synchronous interfacing and LVDS differential signaling up to 840 Mbps.

Stratix devices have embedded SERDES circuitry for serial and parallel

data conversion.

The source-synchronous I/O implemented in Stratix GX devices

optionally includes dynamic phase alignment (DPA). DPA automatically

and continuously tracks fluctuations caused by system variations and

self-adjusts to eliminate the phase skew between the multiplied clock and

the serial data, allowing for data rates of 1 Gbps. In non DPA mode the

I/O behaves similarly to that of the Stratix I/O. This document assumes

that DPA is disabled. However, it is simple to implement the same system

with DPA enabled to take advantage of its features. For more information

on DPA, see the Stratix GX Transceivers chapter in the Stratix GX Device

Handbook, Volume 1.

The fast PLL enables 622.08 Mbps data transmission by transmitting and

receiving a differential clock at rates of up to 645 MHz. The clocks

required in the SERDES for parallel and serial data conversion can be

configured from the received RXCLK (divided down), the TXCLK_SRC

(divided down), or the asynchronous core clock. See

Implementing SFI-4 in Stratix & Stratix GX Devices

Figure

9–4. Stratix devices support source-

Stratix Device Handbook, Volume 2

Figure

9–4.

9–5

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: