EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 693

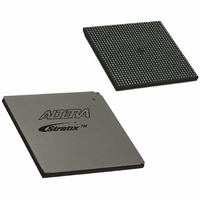

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 693 of 864

- Download datasheet (11Mb)

Altera Corporation

July 2005

Notes to

(1)

(2)

Size (bits)

Parity bits

Byte enable

True dual-port

mode

Embedded shift

register

Dedicated

content-

addressable

memory (CAM)

support

Pre-loadable

initialization with a

.mif

Packed mode

Feed-through

behavior

Output power-up

condition

Table 10–4. Stratix & Stratix GX TriMatrix Memory Blocks vs. APEX II & APEX 20K ESBs

(1)

Features

.mif: Memory Initialization File.

Packed mode refers to combining two single-port RAM blocks into a single RAM block that is placed into true

dual-port mode.

Table

(2)

10–4:

576

Yes

No

No

Yes

No

Yes

No

Rising edge

Powers up

cleared even if

using a .mif

M512 RAM

Table 10–4

Stratix and Stratix GX TriMatrix memory blocks only support pipelined

mode, while APEX II and APEX 20K ESBs support both pipelined and

flow-through modes. Since all TriMatrix memory blocks can be

pipelined, all input data and address lines are registered, while outputs

can be either registered or combinatorial. You can use Stratix and

Stratix GX memory block registers to implement input and output

registers without utilizing additional resources. You can compile designs

containing pipelined memory blocks (inputs registered) for Stratix and

Stratix GX devices without any modifications. However, if an APEX II or

(1)

Stratix & Stratix GX

4,608

Yes

Yes

Yes

Includes support

for mixed width

Yes

No

Yes

Yes

Rising edge

Powers up

cleared even if

using a .mif

M4K RAM

compares TriMatrix memory with ESBs.

Transitioning APEX Designs to Stratix & Stratix GX Devices

(1)

589,824

Yes

Yes

Yes

Includes support

for mixed width

No

No

No

No

Rising edge

Powers up with

unknown state

M-RAM

Stratix Device Handbook, Volume 2

4,096

No

No

Yes

Includes support

for mixed width

No

Yes

Yes

Yes

Falling edge

Powers up

cleared or to

initialized value,

if using a .mif

APEX II ESB

(1)

2,048

No

No

No

No

Yes

Yes

Yes

Falling edge

Powers up

cleared or to

initialized value,

if using a .mif

APEX 20K ESB

10–9

(1)

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: